#### COMPACT INTEGRITY-AWARE ARCHITECTURES

#### BY

#### MICHAEL D. LEMAY

#### **DISSERTATION**

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2011

#### Urbana, Illinois

#### **Doctoral Committee:**

Professor Carl A. Gunter, Chair and Director of Research Professor Sarita V. Adve Assistant Professor Samuel T. King Doctor Peter G. Neumann, SRI International

## **Abstract**

Malware often injects and executes new code to infect hypervisors, OSs and applications on a wide range of systems, from embedded systems to servers in data centers. In this dissertation, we design and evaluate approaches for remotely attesting software integrity and blocking infections on a variety of systems using *integrity kernels*. Existing hardware architectures provide inadequate support for integrity kernels. Despite this, we equip commodity embedded systems with compact integrity kernels. We also describe the limitations of existing non-embedded processors. Then, we develop an extended processor architecture that provides superior isolation, visibility, performance, and compatibility for integrity kernels.

We were the first to demonstrate practical remote attestation for Advanced Metering Infrastructure (AMI), a core technology in emerging smart power grid systems that requires integrity guarantees for each meter over an interval of time rather than just at a given instant. Our prototype *Cumulative Attestation Kernel* (*CAK*) uses less than one quarter of the memory available on 32-bit Atmel AVR32 flash MCUs similar to those used in AMI deployments. We analyze one of the specialized features of such applications by constructing the first formal proof that security requirements are met by a system even when it experiences unexpected, repeated halt conditions, specifically concerning our prototype. We also developed the only remote attestation mechanism for 8-bit Atmel AVR microcontrollers that communicate over networks like those in AMI and that run untrusted application firmware that can be remotely upgraded.

We created the *Integrity-Aware Processor (IAP)*, which is the only processor architecture with direct support for detecting attempts to execute unverified code. Using the IAP as a base, we developed the smallest integrity kernel that checks all code that ever executes in a target Linux system. It uses a network-hosted whitelist.

Soli Deo Gloria

## Acknowledgments

This work was supported in part by DOE DE-OE0000097, NSF CNS 09-64392, NSF CNS 09-17218, NSF CNS 07-16626, NSF CNS 07-16421, NSF CNS 05-24695, NSF CNS 05-24516, NSF CNS 05-09268, NSF CNS 05-5170, ONR N00014-08-1-0248, ONR N00014-04-1-0562, ONR N00014-02-1-0715, DHS 2006-CS-001-000001, HHS 90TR0003-01, and grants from the MacArthur Foundation, Boeing Corporation, and Lockheed Martin Corporation. Michael LeMay was supported on a National Defense Science and Engineering Graduate fellowship from the Air Force Office of Scientific Research for part of this work. The views expressed are those of the authors only.

My advisor, Professor Carl A. Gunter, gave me the freedom to discover and explore my true research passions, even when they fell outside of his core emphases. His intellectual agility enabled him to generate pivotal ideas in our projects regardless of their technical focus. He has actively encouraged and helped me to become a member of the research community and has supported me in my efforts to take our research beyond academia and make it relevant in broader contexts. He encouraged me to take leadership roles soon after I arrived and later challenged me to be a more effective teacher. Finally, he works hard to foster community among the members of his laboratory, both inside and outside of the workplace.

Professor Samuel T. King has been a great source of help and advice throughout my time as a student. I also want to thank the other members of my committee, Professor Sarita V. Adve and Doctor Peter G. Neumann, for their valuable feedback on this work during my preliminary exam, final defense, and on other occasions.

I have greatly enjoyed my collaborations with my labmates, Doctor Jianqing Zhang and Doctor Omid Fatemieh, as well as our discussions and social gatherings. It has been an honor and a privilege to have all of the members of the Illinois Security Lab as associates and friends.

The Trustworthy Cyber Infrastructure for the Power Grid (TCIPG) project as well as its predecessor, the TCIP center, were both critical resources that enabled

me to perform inter-disciplinary research with a group of diverse researchers and that provided me with invaluable connections to industry and government.

My wife, Elizabeth, tirelessly and patiently supported me as I completed my dissertation research. Her love and encouragement helped me to overcome the challenges that the project entailed. I also want to thank my parents, David and Susan LeMay, for their support, encouragement, and advice throughout my education. A special thanks is due to my father for bringing me to his workplace early in my life and demonstrating the joys of engineering to me.

# Table of Contents

| List of T | Tables                                                        | viii |

|-----------|---------------------------------------------------------------|------|

| List of F | Figures                                                       | ix   |

| List of A | Abbreviations                                                 | X    |

| Chapter   | 1 Introduction                                                | 1    |

| 1.1       | Motivation                                                    | 1    |

| 1.2       | Approach                                                      | 3    |

| 1.3       | Contributions                                                 | 7    |

| 1.4       | Dissertation Scope and Organization                           | 7    |

| Chapter   | 2 Background                                                  | 10   |

| 2.1       | Remote Attestation                                            | 10   |

| 2.2       | Advanced Metering Infrastructure                              | 12   |

| 2.3       | Formal Methods                                                | 15   |

| 2.4       | Processor Technologies                                        | 16   |

| 2.5       | Memory Management and Protection                              | 17   |

| Chapter   | 3 Commodity Cumulative Attestation Kernels and Coprocessors . | 19   |

| 3.1       | Threat Model and Requirements                                 | 19   |

| 3.2       | CAK Design                                                    | 22   |

| 3.3       | CAK Implementation and Evaluation                             | 29   |

| 3.4       | CAK Correctness and Fault-Tolerance Analysis                  | 33   |

| 3.5       | Alternate Implementation                                      | 39   |

| 3.6       | CAC Design and Evaluation                                     | 43   |

| 3.7       | Summary                                                       | 52   |

| Chapter   | 4 Architectural Extensions to Support Integrity Kernels       | 54   |

| 4.1       | Threat Model                                                  | 54   |

| 4.2       | Design                                                        | 55   |

| 4.3       | Discussion                                                    | 70   |

| 4.4       | Implementation                                                | 75   |

| 4.5       | Evaluation                                                    | 76   |

| 4.6       | Summary                                                       | 79   |

| Chapter : | 5 Related Work                                             | 81 |

|-----------|------------------------------------------------------------|----|

| 5.1       | Coprocessor-Based Foreign Code Detection                   | 81 |

| 5.2       | Software-Based Foreign Code Detection and Remote Sensor    |    |

|           | Node Recovery                                              | 82 |

| 5.3       | Hypervisor-Based Foreign Code Detection                    | 84 |

| 5.4       | Foreign Code Detection Using Processor Security Extensions | 85 |

| 5.5       | Other Work                                                 | 86 |

| Chapter 6 | 6 Conclusions and Future Work                              | 88 |

| Referenc  | es                                                         | 91 |

## List of Tables

| 2.1 | Temporal modal operators used in LTL formulas               | 15 |

|-----|-------------------------------------------------------------|----|

| 3.1 | Lines of C++ code in each CRAESI kernel component           | 30 |

| 3.2 | Propositions used in LTL formulas to model check integrated |    |

|     | CRAESI design                                               | 34 |

| 3.3 | Lines of C code in each component                           | 51 |

| 4.1 | Comparison of the TCB sizes of various systems              | 77 |

# List of Figures

| 2.1  | Full-featured bidirectional metering network interactions                                                               |    |  |

|------|-------------------------------------------------------------------------------------------------------------------------|----|--|

| 3.1  | Three modes of attack on sensor data available to malicious application firmware running during various lifetime phases |    |  |

|      | occupied by that data                                                                                                   | 20 |  |

| 3.2  | The general CAK program memory layout. The birds represent                                                              |    |  |

|      | "canary" values                                                                                                         | 22 |  |

| 3.3  | A basic state machine representation of CAK operation, in                                                               |    |  |

|      | which transitions are generated by the specified commands                                                               | 24 |  |

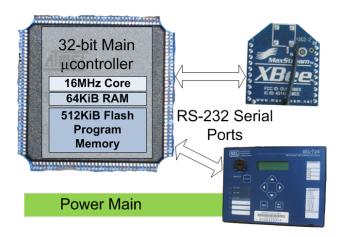

| 3.4  | Prototype hardware components and interconnects                                                                         | 26 |  |

| 3.5  | A performance comparison of TPM-assisted and standalone                                                                 |    |  |

|      | (integrated) CRAESI                                                                                                     | 31 |  |

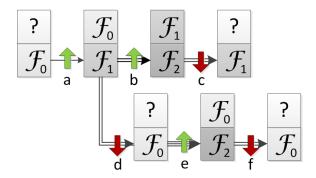

| 3.6  | Representative, legitimate firmware transitions                                                                         | 35 |  |

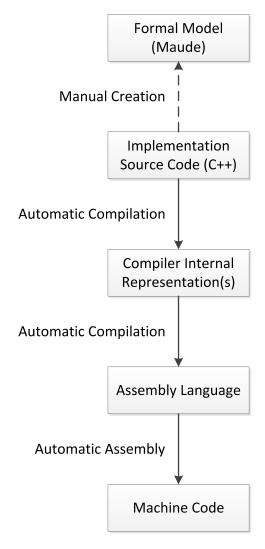

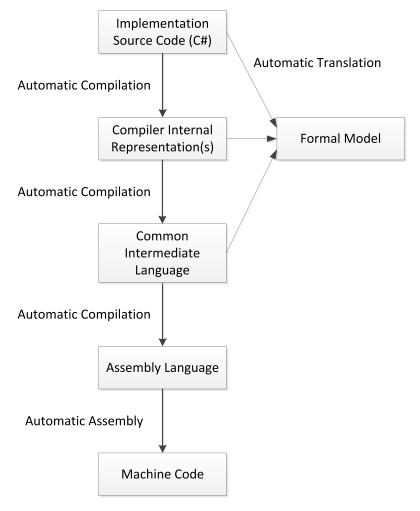

| 3.7  | Manual formal model generation workflow for CRAESI                                                                      | 40 |  |

| 3.8  | Examples of automatic formal model generation workflows                                                                 | 41 |  |

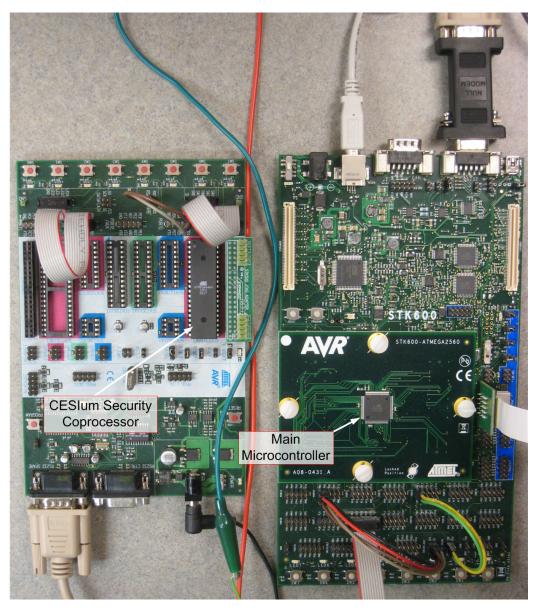

| 3.9  | Hardware prototype of CESIum                                                                                            | 47 |  |

| 3.10 | 1                                                                                                                       |    |  |

|      | based remote attestation                                                                                                | 53 |  |

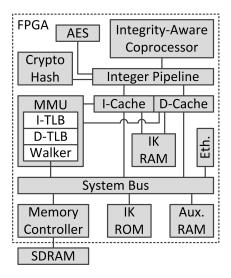

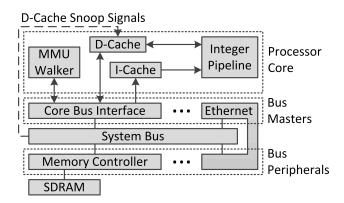

| 4.1  | Internal connectivity of IAP components                                                                                 | 56 |  |

| 4.2  | Connectivity of potential instruction data sources                                                                      | 62 |  |

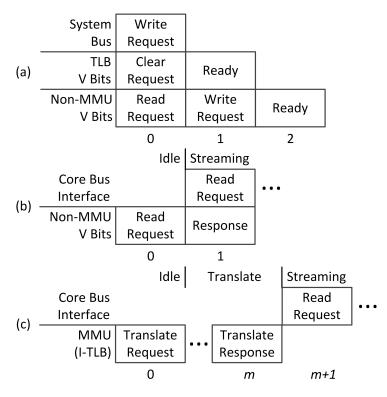

| 4.3  | V bit update timing                                                                                                     | 63 |  |

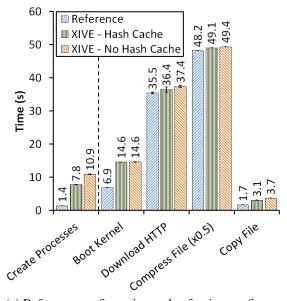

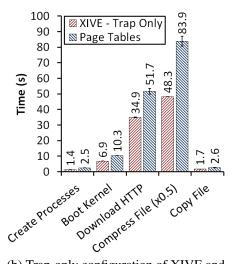

| 4.4  | Mean time required to perform benchmarks, including bars to                                                             |    |  |

|      | show the standard error                                                                                                 | 79 |  |

## List of Abbreviations

AMI Advanced Metering Infrastructure

CAC Cumulative Attestation Coprocessor

CAK Cumulative Attestation Kernel

CCM Counter-CBC MAC (cryptographic mode)

CESIum Cumulative Embedded System Integrity

CFI Control-Flow Integrity

CRAESI Cumulative Remote Attestation for Embedded System Integrity

CTR Counter (cryptographic mode)

DMA Direct Memory Access

DMM Digital Multi-Meter

ECB Electronic Codebook

ECC Elliptic-Curve Cryptography

ECDH Elliptic-Curve Diffie Hellman

FAN Field-Area Network

HAN Home-Area Network

IAP Integrity-Aware Processor

IED Intelligent Electronic Device

IO Input/Output

JIT Just-In-Time

LRU Least-Recently Used

LTL Linear Temporal Logic

MAC Message Authentication Code

MCU Microcontroller Unit

MMU Memory Management Unit

MPU Memory Protection Unit

NIC Network Interface Card

NIDS Network Intrusion Detection System

OS Operating System

PCR Platform Configuration Register

PCS Process Control System

RAM Random Access Memory

ROM Read-Only Memory

SMM (Intel) System Management Mode

SMRAM System Management RAM

TCB Trusted Computing Base

TLB Translation Lookaside Buffer

TOCTTOU Time Of Check To Time Of Use

TOUTTOC Time Of Use To Time Of Check

TPM Trusted Platform Module

VM Virtual Machine

WDT Watchdog Timer

XIVE eXecuting → Verified Enforcer

XNP XIVE Network Protocol

XST Xilinx Synthesis Tool

## Chapter 1

## Introduction

#### 1.1 Motivation

Hypervisors, OSs, and applications continue to be infected by malware [37]. One common result of compromise is the execution of foreign code on the target system. Foreign code can be injected directly into a process as a result of a memory corruption bug, or it can be a separate program that is downloaded and installed on the machine as a part of the attack. Detecting this foreign code is tantamount to detecting the attack. Eliminating this foreign code would severely limit a successful attack.<sup>1</sup>

Remote sensor networks are becoming widespread in critical infrastructure. The networking of these systems often enables firmware to be updated in the field to correct flaws or to add functionality. This capability could potentially be exploited to install malware. A good example of this trend is in the deployment of Advanced Metering Infrastructure (AMI), a centerpiece of "smart grid" technology in which networked power meters are used to collect, process, and transmit electrical usage data, and relay commands from utilities to intelligent appliances. Meters are required to support remote upgrades [1]. Attackers are likely to attempt to compromise the upgrade functionality on AMI devices, since meters have historically been common targets of adversaries seeking to steal electricity [5]. AMI devices may also attract new classes of attackers, given the potential for attacks on AMI to induce large-scale effects. For example, coordinated attacks on demand response systems that use signals from meters to control appliances such as air conditioners may result in blackouts, since the US power grid may operate with a delicate balance between generation and load [17].

It is a best practice to prevent unauthorized firmware (including malware) from being installed on such systems by requiring firmware updates to be digitally signed

<sup>&</sup>lt;sup>1</sup>This chapter includes material from previous publications by LeMay and Gunter [43, 44].

by a trusted authority. However, the principle of defense-in-depth instructs us to include fallback mechanisms to limit the damage that can occur as a result of such protections failing. AMI system administrators can use firmware auditing implemented as remote attestation to detect attacks and respond to them in such a way that they are prevented from inducing large-scale effects. Due to their different key storage structures, vulnerabilities in upgrade access controls and remote attestation are not likely to be closely correlated.

A desktop or mobile system can use a Trusted Platform Module (TPM) to protect and certify audit information concerning its configuration so that it can implement remote attestation [68, 58]. However, TPMs are not ideal for use in many embedded systems. TPMs impose relatively substantial cost, power, memory, and computational overheads on embedded systems. Furthermore, they provide audit data representing a limited time interval, which is incompatible with the deployment model of embedded systems such as advanced meters that operate unattended for extended periods of time.

To address the challenges put forth in this section, this dissertation makes use of integrity kernels, which are operating system kernels that provide foreign code detection or prevention services to the system. Many previous works have also described integrity kernels for various systems. Existing processor architectures for all classes of computer systems do not support integrity kernels as fully as possible. In general, it is often feasible to implement functionality in either software or hardware, with varying effects on the overall complexity of the resultant system. The specific tradeoff decisions embodied in existing processors with state-of-theart security functionality result in integrity kernels that are unnecessarily large and complex. Such processors include at least a Memory Management Unit (MMU) that protects memory based on page tables, an IO-MMU that provides similar protections for IO memory, and often one or more hardware functions specifically intended to create and maintain isolated execution environments for integrity kernels. However, no existing processor directly detects attempts to execute unverified code, which is a core requirement for integrity kernels. This omission along with other limitations implies that all existing mechanisms exhibit deficiencies in some combination of the following requirements:

- 1. **Isolation**, making the integrity kernel vulnerable to compromise.

- 2. **Visibility**, reducing the integrity kernel's capability to detect compromises in the target system.

- 3. **Performance**, making integrity kernels impractical for some applications.

- 4. **Compatibility**, necessitating that the target be substantially modified.

## 1.2 Approach

## 1.2.1 Integrity Kernels for Commodity Microcontrollers

In this dissertation, we first describe two architectures that support remote attestation of advanced meters, which should also serve as an example of how remote attestation could be supported on other similar types of embedded systems. The first architecture is a type of integrity kernel called a Cumulative Attestation Kernel (CAK), which is implemented at a low level in the meter and provides cryptographically secure audit data for an unbroken sequence of firmware revisions that have been installed on the protected system, including the current firmware. This audit data includes a cryptographic hash of the firmware. The CAK itself is never remotely upgraded, so that it can serve as a static root of trust. Our specific objective is to show that CAKs can be practically achieved on flash Microcontroller Units (MCUs). Flash MCUs are distinguished from processors in other types of computers by their onboard flash program memory, which typically contains a monolithic firmware image with a static set of applications that run in a single memory address space. In contrast, higher-end computers often run a full-featured OS such as Linux. Flash MCUs also operate at low clock frequencies and may not offer protection features such as an MMU. We account for these characteristics of flash MCUs in our design.

CAKs must provide high levels of robustness to satisfy the requirements of AMI. For example, their flash memory operations must withstand unexpected, repeated power supply interruptions. This makes CAKs resilient to battery backup failures and even permits them to operate on meters lacking battery backup. We demonstrate that CAKs are able to address these and other relevant requirements using an implementation called *Cumulative Remote Attestation of Embedded System Integrity (CRAESI)* [43]. CRAESI is targeted at a mid-range Atmel AVR32 flash MCU equipped with a Memory Protection Unit (MPU). Since the robustness requirement is unusual, we formally verify that CRAESI is resilient to unexpected, repeated power supply interruptions. This result also implies resilience to some

other types of faults.

We also demonstrate the feasibility of *Cumulative Attestation Coprocessors* (*CACs*) for use with flash MCUs that lack an MPU and have insufficient onboard flash program memory to support a self-contained CAK. Our prototype CAC-based system is called *Cumulative Embedded System Integrity (CESIum)* and incorporates a coprocessor in addition to the main processor, both of which are 8-bit Atmel AVRs. It also uses an external flash memory. The fact that such processors lack substantial memory protection hardware greatly complicates the task of developing an integrity kernel.

We do not extensively discuss node recovery in this dissertation, since it is a distinct field of research, but we note that even recovery can be costly in AMI networks. A node's stored data may be erased during recovery, since the malicious application firmware may have corrupted the data in a way that cannot be detected after the fact. This can imply a massive loss of data on a large AMI network that could cause significant revenue loss to a business dependent on that data. By permitting individual infected nodes to be identified, and uninfected nodes to be definitively validated, cumulative attestation can minimize this revenue loss.

## 1.2.2 Custom Hardware to Support Integrity Kernels

We demonstrate that it is possible to dramatically reduce the complexity of an integrity kernel by adding a modest amount of hardware to a processor to directly support monitoring and isolation tasks that otherwise would have required substantial manipulations of the more general hardware protection mechanisms that are present in existing processors. The hardware extensions are sufficiently powerful that the integrity kernel built on top of them prevents foreign code from executing at all in a full-featured SPARC Linux system. One way to prevent foreign code from running on a system is to whitelist the code in legitimate applications and refuse to run any code that is not on this whitelist, thus enforcing the  $eXecuting \rightarrow Verified$  property on all code. This conceptually straightforward approach has been difficult to implement in practice. It is challenging both to identify legitimate applications and to enforce the resultant whitelist. We assume that legitimate applications are known in advance and focus on enforcement in this dissertation.

Many existing integrity kernels<sup>2</sup> rely on virtualization implemented using an MMU. They manipulate page tables to cause a trap to the hypervisor whenever an unverified page in a Virtual Machine (VM) is about to be executed [60, 47]. Popular virtual machines provide many features, but have correspondingly large Trusted Computing Bases (TCBs) (e.g. ~ 230K lines of code in Xen [10]) that may be unable to enforce isolation. Even target systems that can use minimalistic, security-oriented hypervisors may suffer from virtualization-related performance degradation. Furthermore, some virtualization approaches require substantial changes in the target system's code to make it compatible with the hypervisor.

Intel System Management Mode (SMM) can be used to overcome some of these limitations, since it provides hardware separate from the MMU to set up an isolated execution environment [10, 71]. However, the confidentiality and integrity of SMM handlers can be tricky to guarantee due to the complex interactions between the various system components involved in implementing SMM [24]. Furthermore, some system state is invisible in SMM, and SMM can only be triggered by a few types of events, such as an electrical signal at a processor pin or a write to a specific IO location. Code has been observed to execute about two orders of magnitude more slowly in SMM compared to protected mode.

We propose a new hardware mechanism that addresses the limits of other approaches. The *Integrity-Aware Processor (IAP)* is an extended SPARC processor that provides an isolated execution environment for an integrity kernel that can enforce eXecuting → Verified or provide other functionality [44]. Although the integrity kernel shares many processor resources with the target, IAP stores the integrity kernel in a completely separate address space from the target and does not permit the target to initiate any data transfers between the two spaces. On the other hand, the integrity kernel has full visibility into the target. IAP stores the entire integrity kernel on-chip to minimize access latency. Thus, integrity kernel code runs at least as fast as code in the target system, and it can be invoked with the same overhead as a native trap handler. IAP also incorporates hardware accelerators for essential cryptographic primitives.

IAP transfers control to the integrity kernel in response to several configurable conditions, including attempts by the processor to execute code that has not been verified by the integrity kernel. It includes hardware structures to track code that

<sup>&</sup>lt;sup>2</sup>For the sake of consistency, we use the term "integrity kernel" to refer to all code that runs on the processor hosting the target OS and is involved in detecting and preventing the execution of foreign code, although some of that code would not ordinarily be considered part of a kernel.

has been verified and to detect attempts to modify it after it has been initially verified, subsequently causing it to be re-verified before it is re-executed. IAP monitors individual pages of memory in the virtual address space of each process, or the physical address space when the MMU is disabled. These features permit the integrity kernel to enforce eXecuting  $\rightarrow$  Verified without relying on the configuration of the MMU page tables, further simplifying the TCB.

We developed the *eXecuting*  $\rightarrow$  *Verified Enforcer* (*XIVE*) to demonstrate the extent to which IAP can reduce the TCB of the integrity kernel. The XIVE whitelist is located on a centralized *approver* connected to the network, to minimize the complexity of the XIVE kernel and to simplify whitelist updates. We implemented XIVE for an IAP end node based on a Field-Programmable Gate Array (FPGA), the approver on a commodity Linux host, and connected the two using 100Mbps Ethernet. The XIVE kernel contains 859 instructions, and successfully protects a Linux target system that has been slightly modified so that it is efficient to monitor and so that it tolerates sharing its physical network interface with the XIVE kernel.

Although they demonstrate some of the challenges that integrity kernels on commodity architectures must overcome, CRAESI and CESIum are not directly comparable to XIVE. CRAESI simply monitors all code that the target system executes, rather than checking it against a whitelist ahead of time. However, XIVE can be easily modified to also support this model if it is useful in a particular environment. CRAESI and CESIum also place more restrictions on the software that they support than XIVE. Some of these restrictions are imposed by the commodity flash MCUs themselves. For example, the types of MCUs targeted by CESIum do not support executing code from RAM. Although the types of MCUs targeted by CRAESI do support that, CRAESI prevents it from occurring. CESIum and CRAESI both view the entire application firmware as a monolithic image, which is consistent with the usage model of remote sensor nodes. In contrast, XIVE controls programs on a page-by-page basis and recognizes individual programs. XIVE also permits limited changes to be made to the executable pages of programs. The restrictions imposed by CRAESI and CESIum simplify their protection mechanisms, but reduce their generality and applicability to systems outside the field of remote sensor networks.

## 1.3 Contributions

We make the following contributions in the area of integrity kernels for commodity microcontrollers:

- We develop CRAESI, the first technology to support remote attestation for mid-range flash MCUs in remote sensor networks, which are subject to high jitter and permit sensors to collude with external computers. CRAESI's threat model admits malicious application firmware. We implemented it as a CAK that leverages the moderately-sized flash memory and MPU of an Atmel AVR32 MCU without requiring a coprocessor.

- We present a formal proof that CRAESI has certain security and faulttolerance properties. We accomplish this using the Maude model checker. This is the first formal proof that a system is tolerant to power supply interruptions.

- We develop CESIum, the only approach to remote attestation for remotely-upgradeable, low-end flash MCUs in remote sensor networks that is invulnerable to control-flow attacks launched by malicious application firmware. It incorporates a security coprocessor and an external flash memory.

We make the following contributions in the area of integrity kernels for an extended processor architecture:

- We develop IAP, the only processor architecture with hardware support for directly detecting attempts to execute unverified code.

- We develop the XIVE kernel for IAP, the most compact integrity kernel that is capable of enforcing eXecuting → Verified.

## 1.4 Dissertation Scope and Organization

We investigate *compact integrity-aware architectures* in this dissertation. That investigation involves hardware, software, and firmware components, as well as formal proofs. The size of a system can be measured in several ways. Like many other works, this dissertation primarily uses source lines of code as the metric. In general, a compact system can be expected to exhibit fewer security vulnerabilities

than a larger system, assuming that the two systems have similar characteristics such as their implementation and verification techniques, their overall purpose, and their history of usage and testing [4]. Furthermore, compact systems are generally more amenable to formal verification [7]. Additionally, binary compactness is important for integrity kernels on embedded systems, because those systems have severe resource limitations. Our thesis is:

It is possible to develop compact integrity kernels to protect commodity microcontrollers in remote sensor networks, and a custom hardware architecture can enable the construction of compact integrity kernels with superior isolation, visibility, performance, and compatibility.

Chapter 2 contains background material that is helpful in understanding the rest of the dissertation. It contains information on remote attestation, AMI, formal verification, and processor technologies.

Chapter 3 discusses integrity kernels for commodity microcontrollers. The CRAESI CAK for the Atmel AT32UC3A0512 AVR32 microcontroller is implemented using C++ and is situated within a prototype that emulates an advanced electric meter. We use the Maude model checker to formally verify that CRAESI correctly implements core security functions related to audit log maintenance and that it properly updates its audit log and internal filesystem in the presence of repeated, unexpected power supply interruptions, provided that the power supply is eventually restored for a sufficient period of time. The CESIum CAC-based system uses an Atmel ATmega644V AVR microcontroller as a security coprocessor that monitors the main microcontroller, an Atmel ATmega2560 AVR. The firmware for both microcontrollers is implemented using C and assembly language. The prototype also incorporates an external flash memory.

Chapter 4 presents our extended processor architecture, IAP, and discusses integrity kernels for that architecture. IAP uses the LEON3 SPARC soft core as the basis for a prototype. It is synthesized from VHDL for use on an FPGA. The XIVE integrity kernel is written entirely in SPARC assembly language and is more isolated, comprehensive, and compatible than other integrity kernels that are capable of enforcing eXecuting → Verified. XIVE monitors all of the code that is executed by a Linux target system running on IAP. We evaluate the performance of a prototype system based on the XIVE kernel and a network-based whitelist server we developed using multi-threaded C++ on Linux and show that it is adequate. We also show that IAP imposes less overhead on integrity kernels compared to other processors.

Chapter 5 compares our approaches to those in related work. It covers works that rely on coprocessors, software, hypervisors, and processor extensions to implement integrity kernels.

Chapter 6 summarizes our contributions and proposes future work.

## Chapter 2

## Background

This chapter discusses background material that is helpful for understanding the rest of this dissertation. It briefly explains remote attestation. Next, it describes the nature, scale, and motivations of ongoing AMI deployments, as well as anticipated benefits from AMI. Then it provides a brief introduction to formal verification using Maude. Finally, it discusses relevant processor technologies and the memory management and protection mechanisms that they provide.<sup>1</sup>

## 2.1 Remote Attestation

Remote attestation is a process whereby a remote verifier  $\mathcal{V}$  can obtain certified measurements of parts of the state of a system C. A variety of protocols can be used to accomplish this. They usually involve at least two messages. The request  $\mathcal{V} \xrightarrow{\langle \nu \rangle} C$  contains a nonce  $\nu$  used to ensure the freshness of the attestation results. The response  $C \xrightarrow{[\langle \nu, \sigma \rangle]_{RTMC}} \mathcal{V}$  is digitally signed by the Root-of-Trust for Measurement (RTM) of C (RTMC) to certify that it has not been tampered, and contains the nonce  $\nu$  as well as a record of the system's state  $\sigma$ . Of course, this assumes that the system contains some RTMC that is capable of securely recording and certifying the system's state. On desktop PCs, the TPM and supporting components in the system software often fulfill this role.

A TPM is typically a hardware security coprocessor that comprises several internal peripherals coordinated by a central microcontroller core [68]. It is intended to be difficult to remove from the platform in which it was originally installed. It is also designed to make physical tampering evident upon subsequent physical inspection. The TPM contains several keypairs. Two of them can be used to digitally sign internal registers that contain cryptographic hashes. These registers

<sup>&</sup>lt;sup>1</sup>This chapter includes material from a previous publication by LeMay, Gross, Gunter, and Garg [42]. It also includes material from a previous publication by LeMay and Gunter [43].

are called Platform Configuration Registers (PCRs). The TPM implements an "Extend" function that requires a hash value as a parameter and then updates the hash value in a particular PCR by appending the new hash to the old PCR value, hashing the result, and storing it in the PCR. The OS on *C* maintains a log of information that can be used to evaluate its configuration and state and performs an extend operation to commit each new log entry as it is added. To generate a trustworthy attestation using the basic protocol described above, the main processor on *C* must send the nonce to the TPM and request that it digitally sign ("Quote") the PCRs. The processor is assumed to not have the capability to forge these signatures, since the TPM's private keys are never released by the TPM unless it is physically compromised. Therefore, for the protocol to proceed, the TPM must return the signed attestation data to the processor, and the processor must then return that signature along with the log that is required to interpret the attestation to *V*. The TPM contains many other structures to support true random number generation, cryptography, and other functions.

Well-designed systems include multiple layers of protections to prevent compromises, including access controls for installation privileges and signatures on code that are verified before installation. Remote attestation provides an additional layer of defense in the event that these protections fail, hence providing defense-indepth. This is similar to the synergistic relationship between Network Intrusion Detection Systems (NIDSs) and firewalls. A NIDS detects attacks that bypass firewalls, leading to faster attack recovery and a subsequent strengthening of firewall rules. These mechanisms work well together because of their distinct failure modes. Typical upgrade controls that require firmware to be signed can be compromised if the private keys used to sign firmware are compromised, or the upgrade controls are bypassed by a buffer overflow or other type of attack. Modern embedded systems can run complex software stacks that may be vulnerable to attacks similar to those that have plagued server and desktop machines. Even if a different key is used to sign firmware upgrades for each node on a network, those private keys are all likely to be stored in a central repository. The compromise of the repository could lead to the compromise of all systems on that network. In contrast, CAKs and CACs store their private keys within individual meters that are geographically scattered, greatly increasing the cost of compromising large numbers of private keys. Only the availability and authenticity of the corresponding public keys must be ensured to provide secure auditing capabilities. This is generally a more tractable problem than ensuring long-term confidentiality of a centralized private key repository.

Even if a system is never compromised, remote attestation is useful when multiple parties are authorized to upgrade or use the system and they must be able to verify that the configuration changes made by other parties are acceptable. For example, government regulators could query an advanced meter to obtain an unforgeable guarantee that it is using firmware that provides accurate meter readings.

## 2.2 Advanced Metering Infrastructure

Advanced electric meters are embedded systems deployed by utilities in homes or businesses to record and transmit information about electricity extracted from the power distribution network and potentially to support more advanced functionality. They arose out of automated meter reading, which simply involves remote collection of meter data. However, AMI can support new applications based on bidirectional communication, such as the ability to manipulate power consumption at a facility by sending a price signal or direct command to its meter (demand response). AMI networks are being deployed on a massive scale [5]. A report by Pike Research states that more than 250 million meters will be deployed worldwide by the year 2015 [57]. AMI is a particularly good example of a remote sensor network and a good benchmark for study because of its nascent but real deployment and rich set of requirements.

The sophisticated functionality of advanced meters creates numerous attack scenarios and increases the likelihood that they will contain security vulnerabilities linked to firmware bugs. An outage of the meters in a region could entail a huge financial loss for a utility. The "Guidelines for Smart Grid Cyber Security" published by NIST specifically call for remote attestation of smart grid components [1]. In a previous work we further motivated the use of attestation to provide AMI security [42].

Other embedded systems could also benefit from CAK-supported intrusion detection. Intelligent Electronic Devices (IEDs) used in electrical substations to monitor and control the transmission and distribution of electricity often support remote firmware upgrades and can exert more direct control over the flow of electricity than demand-responsive meters [29].

We now provide additional details on AMI. In the future, it will afford a number of potential advantages to energy service providers, their customers, and many other entities [28]:

- 1. **Customer control:** Customers gain access to information on their current energy usage and real-time electricity prices.

- 2. **Demand response:** Power utilities can more effectively send control signals to advanced metering systems to curtail customer loads, either directly or in cooperation with the customer's building automation system.

- 3. **Improved reliability:** More agile demand response can improve the reliability of the distribution grid by preventing line congestion and generation overloads. These improvements could also reduce the strain on the transmission grid.

There are several distinct categories of advanced metering systems that support the functionality discussed above with varying degrees of success. The least capable systems use short-range radio networks and may be less expensive to deploy initially, but they require readers to drive by in vans to read the meters. More capable systems support unidirectional network communication from the meter data management service, and the most capable systems have fully bidirectional network connections with the meter data management service. We focus on meters with bidirectional connections in this dissertation. AMI networks with connectivity to the meter data management service can distribute real-time pricing schedules to meters, which can influence customer behavior and induce manual or automatic demand response actions [15]. They can also support direct control signals.

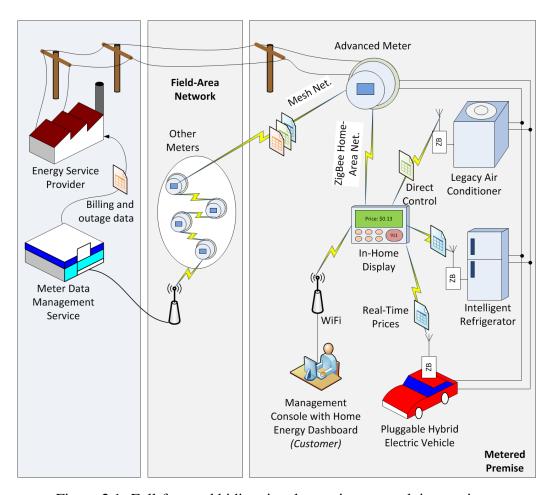

In Figure 2.1, we show how a full-featured bidirectional metering network could be organized. The network is divided into two main domains that are connected via a Field-Area Network (FAN). The first domain houses the meter data management service and the energy service provider that controls the physical delivery of electricity. The second domain comprises the metered premises, which may have mesh network connections between themselves to extend the overall reach of the AMI network. Each of these premises may also be equipped with a Home-Area Network (HAN) containing an in-home display, which interacts with the meter and intelligent appliances and perhaps a home energy dashboard that provides complementary features to those of the in-home display. We have investigated the challenges involved in coordinating such a complex network and proposed a hierarchical approach that accounts for the various levels of functionality present in various devices within the HAN [45].

Figure 2.1: Full-featured bidirectional metering network interactions.

| Operator                     | Name               | Description                                                                                     |

|------------------------------|--------------------|-------------------------------------------------------------------------------------------------|

| $\bigcirc \varphi$           | Next               | $\varphi$ holds in the next state.                                                              |

| $\varphi  \mathcal{U}  \psi$ | Until              | $\psi$ holds in the current or a future state, and $\varphi$ holds until that state is reached. |

| $\Diamond \varphi$           | Eventually         | $\varphi$ holds in some subsequent state.                                                       |

| $\Box \phi$                  | Henceforth         | $\phi$ must hold in all subsequent states.                                                      |

| $\varphi W \psi$             | Unless             | $\varphi$ holds in all states until $\psi$ holds, or forever if $\psi$ is never satisfied.      |

| $\varphi \Rightarrow \psi$   | Strong Implication | $\psi$ holds in any state in which $\varphi$ is satisfied.                                      |

Table 2.1: Temporal modal operators used in LTL formulas.

## 2.3 Formal Methods

Formal methods are used to verify correctness and fault-tolerance properties of CRAESI in §3.4. Specifically, model checking is a methodology for systematically exploring the entire state space of a model and verifying that specific properties hold over that entire space. Maude is the name of a language as well as a corresponding tool that supports model checking based on rewriting logic models and Linear Temporal Logic (LTL) properties [21]. Essentially, rewriting logic provides a convenient technique to express non-deterministic finite automata. Maude is a multi-paradigm language, and supports membership equational logic, rewriting logic, and even has a built-in object-oriented layer. We use Maude for our verification tasks.

Maude provides a search function that can be used to explore all distinct states that can be reached from an initial state. The search command can be parameterized to only display states that satisfy a particular property, and this can be used to perform basic model checking. This is only suitable when the desired state can be identified by a simple set of propositions combined using logical connectives  $(\neg, \land, \lor, \rightarrow)$  on that state, not considering any preceding states. Appropriate propositions must be defined for the particular model under consideration.

For more sophisticated model-checking operations, theorems and lemmata can be formalized using LTL. An LTL formula is a predicate over a sequence of states. Each formula comprises propositions that are connected with logical connectives and the temporal modal operators described in Table 2.1.

## 2.4 Processor Technologies

We deal with several processor technologies in this dissertation, with a special emphasis on flash MCUs and FPGAs. We describe the relevant characteristics of these technologies in this section and compare them against others.

The flash MCUs in this dissertation are commodity processors that incorporate a microprocessor core, data RAM, flash program memory, EEPROM persistent data memory, clock generation circuitry, and peripherals such as various serial and memory interfaces, analog-to-digital converters, etc. They are essentially complete computers in a single chip, lacking only a power supply and connections to devices that enable them to meaningfully interact with the physical world. Another way to think of a flash MCU is as a single chip that contains analogous components for most of the items found inside the case of a typical desktop PC. A PC requires connections to a monitor, keyboard, power cord, and perhaps other devices to do useful work, just as flash MCUs are reliant on external components to interact with the physical world. However, flash MCUs have very limited capabilities and low levels of performance, because they target applications with tight energy and cost constraints. A wide variety of flash MCUs are currently available, based on 8-bit through 32-bit instruction set architectures. The security features in these designs also vary widely, with some providing simple support for isolating a bootloader from an application and others featuring MPUs that support separate privilege levels and fine-grained memory access controls.

Most processors today, including flash MCUs, are manufactured as Application Specific Integrated Circuits (ASICs), which means that their designs are etched into silicon in such a way that they implement a single circuit design that provides processor functionality. An alternative approach to implementing processors uses FPGAs, which are chips that can be reconfigured many times to implement different circuits. ASICs have many advantages over FPGAs that justify their popularity in spite of their inflexibility. For example, an FPGA consumes more area, energy, and time to perform a computation compared to an ASIC. However, FPGAs are very useful for performing processor design research and can even be used in certain applications that are not sensitive to the drawbacks of FPGAs. FPGAs are also being combined with ASICs in some cases to provide benefits from both processor technologies.

FPGAs must be configured to implement a particular circuit using a bit file, which can be generated from a Hardware Description Language (HDL). Verilog

and VHDL are popular HDLs. A hardware design encoded in an HDL can represent the hardware's circuit at various levels of abstraction. It resembles the source code of a software program in many ways, and can even contain sequential statements similar to those in source code from an imperative software programming language. However, the bit file is not analogous to a binary program comprising a sequence of instructions. The HDL source code undergoes a multi-step process that ultimately transforms it into the bit file, which represents a low-level configuration of the individual circuit elements within the FPGA that will then implement the desired overall circuit. When the bit file contains the configuration information to implement an entire processor within the FPGA, we refer to that processor as a "soft core."

## 2.5 Memory Management and Protection

Some of the processors in this dissertation primarily rely on an MPU or MMU to protect and manage memory accesses from software. This section describes the basic concepts underlying these mechanisms as they are implemented in the specific processors in this dissertation.

An MPU is simpler than an MMU and simply defines and controls access to regions of memory. Note that it does not perform any mapping of memory addresses. The OS configures the MPU to divide the processor's physical address space into various regions, and to control access to those regions according to the current mode of the processor when it is executing software. For example, the software may be allowed to read, write, and execute some region of memory when it is executing in supervisor mode, as would be the case when the operating system kernel is active. It could be restricted so that it is only able to read that region when it is executing in user mode.

An MMU maps addresses in a virtual address space to physical addresses that correspond to physical memory locations and also enforces access controls during that process. These mappings are defined using page tables. Page tables are arranged hierarchically and terminate in page table entries that either reference a specific page of physical memory or are invalid, indicating an undefined region of virtual addresses. To map a virtual address to a physical one, the processor performs an iterative process to walk through these page tables until it reaches a page table entry. At each step, it uses a specific portion of the original virtual

address to perform the lookup to identify either the page table entry or the pointer to the next page table. Once a valid page table entry has been accessed, the processor combines it with the remaining portion of the original virtual address and uses that as the physical address. Walking through page tables is an expensive process, so the processor caches recently-accessed page table entries in structures called Translation Lookaside Buffers (TLBs). If the page table walker encounters an invalid page table entry or one that does not permit the requested type of access, it generates a trap to the OS.

Operating systems typically allocate a separate virtual address space for each process. Thus, it is not sufficient for the various caches in the processor (including TLBs) to simply label entries with virtual addresses, since multiple processes may use identical virtual addresses to refer to different physical addresses. The processes may also be assigned different permissions for the same address. To deal with this issue, the processor associates a unique context value with each process, and includes that context value in each cache entry that is created when the process is active.

## Chapter 3

# Commodity Cumulative Attestation Kernels and Coprocessors

We demonstrate in this chapter that we can develop compact integrity kernels for commodity flash MCUs, and that those integrity kernels exhibit good performance compared to well-known alternative approaches. We accomplish this by first presenting a threat model and a set of requirements in §3.1 for these integrity kernels. Second, we propose a design that satisfies those requirements on a flash MCU with a modest amount of flash memory and an MPU in §3.2. We present results from an experimental evaluation of a prototype implementation of that design, called CRAESI, in §3.3. We then formally analyze CRAESI with respect to important fault-tolerance and correctness properties in §3.4, using the Maude model checker.

CRAESI is not applicable to flash MCUs that have a small amount of flash memory or lack an MPU. However, such MCUs are still used in security-critical environments. Thus, we discuss how the design of CRAESI can be adapted to support such MCUs in §3.6. We also evaluate the performance of the adapted design on a prototype system called CESIum.<sup>1</sup>

## 3.1 Threat Model and Requirements

#### 3.1.1 Threat Model

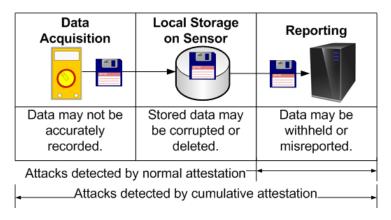

Data integrity on meters can be compromised by malicious application firmware in various ways, as shown in Figure 3.1. Actuator controls can also be abused. A typical remote attestation scheme provides evidence of the integrity of data (such as firmware) at the time an attestation report is requested. Such a system is vulnerable to what one might call Time-Of-Use-To-Time-Of-Check (TOUTTOC) inconsistencies (dual to the more familiar Time-Of-Check-To-Time-Of-Use (TOCTTOU)

<sup>&</sup>lt;sup>1</sup>This chapter includes material from a previous publication by LeMay and Gunter [43].

Figure 3.1: Three modes of attack on sensor data available to malicious application firmware running during various lifetime phases occupied by that data.

inconsistencies) wherein data was inaccurately recorded, corrupted, or deleted, or actuator controls were abused, before the time of attestation if the system was subsequently reset. In contrast, cumulative attestation detects such attacks.

We assume that an attacker is capable of communicating with a protected system over a network and installing malicious application firmware. We also assume that the attacker has a priori knowledge of the layout of the kernel's code and data memory spaces, as well as their static contents, but not the contents of dynamic variables and static values that vary between kernels.

"Ordinary" environmental phenomena must not cause any of the security requirements of the kernel to be violated. An example is an accidental power supply interruption, unless the system has a robust, trusted power supply. On the other hand, a bit flip caused by cosmic radiation would be considered an extraordinary phenomenon in most ground-based embedded systems. These examples make it clear that the definitions of ordinary and extraordinary will vary based on a system's intrinsic characteristics and its environment. In this paper, we only include accidental power supply interruptions in our threat model, although we discuss other types of faults that have similar effects and are therefore handled by the same fault-tolerance mechanisms. We also exclude physical attacks on microcontrollers such as fault analysis, silicon modifications, and probing [6, 31]. The use of a CAK does not exclude tamper-resistance, but CAKs address remote attacks rather than local, physical attacks which are generally much more expensive than remote attacks. Large-scale remote attacks potentially enable different classes of attack outcomes (such as blackouts in our example).

The security of remote attestation based on a CAK depends upon the fact

that application firmware runs at a lower privilege level than the CAK and is not permitted to access security-critical memory and peripherals. This excludes a wide variety of attacks, such as Cloaker [22]. The specific peripherals that are considered security-critical will vary between microcontrollers.

Note that a CAK does not detect attacks that succeed by simply modifying data RAM. Although data RAM is not executable by the application, corruption in data RAM can lead to system compromises in other ways [34]. However, it is prohibitively expensive to record changes to data RAM. It is also more challenging to characterize all legitimate values of data RAM. This limitation implies that return-oriented programming can potentially be used to corrupt the control flow of an audited firmware image to implement an attack. However, it can be more difficult to construct a return-oriented program than it is to construct a program intended for native execution. For example, the targeted firmware must contain a sufficient set of "gadgets" to implement the desired attack [30].

## 3.1.2 Requirements

The basic security and functional requirements for a CAK are that it maintain an audit log of application firmware revisions installed on a meter, and that it make a certified copy of that log available to authorized remote parties that request it. It must satisfy the following properties to provide security: 1) Comprehensiveness: The audit log must represent all application firmware revisions that were ever active on the system. Application firmware is considered to be active whenever the processor's program counter falls somewhere within its installed code space. 2) Accuracy: Whenever application firmware is active, the latest entry in the audit log must correspond to that firmware. The earlier entries must be chronologically ordered according to the activation of the firmware revisions they represent.

We define the following requirements for a CAK based on the characteristics and constraints of advanced meters:

- 1. **Cost-effectiveness:** Even the smallest added expenses in advanced meters become significant when multiplied for massive deployments.

- 2. **Energy-efficiency:** Some embedded systems are critically constrained by limited energy supplies, often provided by batteries. Although meters are attached to mains power, they may be constrained to low energy consumption to reduce energy costs.

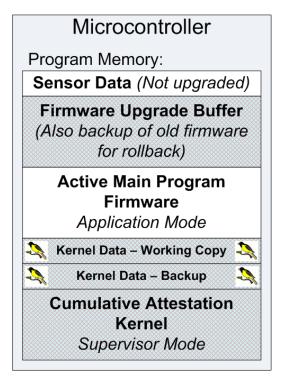

Figure 3.2: The general CAK program memory layout. The birds represent "canary" values.

3. **Suitability for hardware protections:** The CAK must be adapted to the protection mechanisms provided by the processor on which it runs.

## 3.2 CAK Design

We now present a kernel design that satisfies the requirements. The basic flash memory layout of the system is depicted in Figure 3.2. The executable code for the CAK is located at the beginning of memory, where bootloaders are usually stored. Above that, two redundant regions are used to store data used by the kernel. The *Installed Region* is the only memory containing instructions that can be executed in user mode. The *Upgrade Region* is used to buffer firmware upgrades. Finally, *Sensor Data* can potentially be used by the application to store arbitrary non-executable data.

The content of each *Kernel Data* section is divided into several regions, and contains the following:

## 3.2.1 Audit Log

Each audit log entry is denoted as  $\epsilon_i = \langle \tau, \eta, \theta \rangle$ , where  $\tau \in \{hash, chain\}$  specifies the type of the entry,  $\eta$  specifies the event that caused  $\epsilon$  to be recorded in the log if it was not recorded as a result of a successful upgrade, and  $\theta$  is a hash value  $h(\mathcal{F}_i)$  if  $\tau = hash$  and  $\mathcal{F}_i$  is the currently installed firmware image, or a hash chain if  $\tau = chain$ . The audit log  $AL = (\epsilon_0, \epsilon_1, \dots \epsilon_{n-1})$  when |AL| = n such that  $\mathcal{F}_i$  was installed immediately after  $\mathcal{F}_{i-1}$ . It is possible for AL to overflow memory, so it can be divided into two lists  $AL_{ovf} = (\epsilon_0, \epsilon_1, \dots \epsilon_m)$  and  $AL_{recent} = (\epsilon_{m+1}, \epsilon_{m+2}, \dots \epsilon_{n-1})$ . The maximum length of  $AL_{recent}$  is dictated by the capacity of the flash. When it overflows, the entry  $\epsilon_{chain} = \langle chain, none, h(h(\dots ||\epsilon_{m-1})||\epsilon_m) \rangle$  is included in the audit log memory region, where || is used to indicate concatenation. Its hash value represents a left fold of  $AL_{ovf}$  with the function  $h_{fold}(x, y) = h(x||y)$ .  $AL_{inmem} = AL$  when  $|AL_{ovf}| = 0$  and  $AL_{inmem} = (\epsilon_{chain}) + AL_{recent}$  otherwise. A counter  $\lambda = |AL|$  is also included.

If AL has overflowed, the remote party performing the attestation must already know  $(h(\mathcal{F}_0), h(\mathcal{F}_1), \dots h(\mathcal{F}_m))$ . This is a reasonable assumption if the embedded system is used by a group of remote parties that can communicate with all parties that have installed new firmware revisions on the system. In that case, the party verifying the attestation can request that the updaters provide whatever hash values the verifier does not yet know. It can then verify the current hash chain.

## 3.2.2 Asymmetric Keypairs

The public and private keys for keypair  $P_x$  are denoted as  $Y_x$  and  $R_x$ , respectively.  $R_{\mathcal{F}}$  is used to sign the firmware audit log during attestation operations.  $P_{DH}$  is used during Diffie-Hellman key exchanges.  $R_{\Omega}$  is used to sign  $Y_{\mathcal{F}}$  and  $Y_{DH}$ . It is generated by the CAK using its built-in random number generator when it is first started and stored in memory, or burned into fuses at the factory in such a way that no entity, including the manufacturer, can determine its value. Counters  $\lambda_{\{\mathcal{F},DH,\Omega\}}$  are used to record the number of signatures generated by the corresponding private keys.  $P_{\mathcal{F}}$  and  $P_{DH}$  will be individually refreshed when their associated counters reach a threshold value.

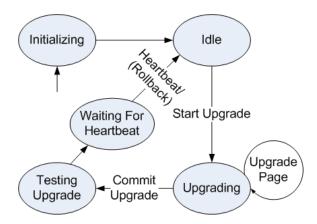

Figure 3.3: A basic state machine representation of CAK operation, in which transitions are generated by the specified commands.

#### 3.2.3 System State

An explicit state variable  $\sigma$  is used to control transactions. States in the automata in Figure 3.3 illustrate the possible values of  $\sigma$ .

The CAK satisfies the Comprehensiveness and Accuracy requirements by controlling all access to the low-level firmware modification mechanisms in the system. The state machine in Figure 3.3 manages the application firmware upgrade process within the CAK. The transition labels not in parentheses are commands that can be issued by the application to cause itself to be upgraded. The current state is recorded in  $\sigma$ . The "Waiting for Heartbeat" state causes the application firmware to be reverted to its previous revision if no heartbeat command is received within a certain period of time. Any unexpected command received by the CAK will be ignored.

Three additional commands not shown in the figure can be executed by an application to: 1) Quote: digitally sign and transmit a copy of  $AL_{inmem}$ , including a nonce for freshness, 2) Retrieve Public Keys: retrieve  $P_{\mathcal{F}}$ ,  $P_{DH}$ ,  $P_{\Omega}$  signed using  $R_{\Omega}$ , and 3) Handshake: perform a Diffie-Hellman key exchange. The Handshake command demonstrates how the asymmetric cryptography implemented within the kernel can be used to perform operations directly useful to the application (establish a symmetric key with a remote entity, in this case), to defray the memory space that the CAK requires. More general access could be provided in future designs, but would complicate the security analysis of the API.

Transactional semantics must be provided for all the persistent data used by the kernel. This design accomplishes that by maintaining redundant copies of all persistent data in a static "filesystem"  $FS = \langle \gamma_0, \Phi_w, \gamma_1, \gamma_2, \Phi_p, \gamma_3 \rangle$  where each  $\gamma_i$  ( $i \in \{0, 1, 2, 3\}$ ) is a Boolean "canary" flag, and  $\Phi_w$  and  $\Phi_p$  are tuples of the form  $\langle \sigma, P_{\mathcal{F}}, \lambda_{\mathcal{F}}, P_{DH}, \lambda_{DH}, P_{\Omega}, \lambda_{\Omega}, \sigma_{upg}, AL_{inmem} \rangle$ , where  $\sigma_{upg}$  encodes the state of the upgrade process, as explained below. The tuple  $\Phi_w$  is a working copy that is modified by the kernel and  $\Phi_p$  is a persistent copy that provides redundancy. The working copy update process is described in Listing 1.

It is more conventional to represent a filesystem as a relation between filenames and data, and in fact we use that representation in our formal analysis of this filesystem's fault tolerance in §3.4. In that case,  $FS \subset FN \times FD$  where FN is the set of filenames and FD is the set of all possible file data values.

```

Listing 1 Update filesystem working copy.

```

```

procedure FsStore(addr, data)

\gamma_0 \leftarrow False \\

\gamma_1 \leftarrow False \\

\Phi_w \leftarrow \text{Insert}(addr, data, \Phi_w) \\

\gamma_0 \leftarrow True \\

\gamma_1 \leftarrow True

end procedure

```

The copies of the filesystem have canary values  $\gamma_i$  before and after the file data as depicted in Figure 3.2. Whenever a file in the working copy is modified, canaries  $\gamma_0$  and  $\gamma_1$  are first invalidated and then re-initialized after the file has been written. An unlimited number of modifications can be made to the working copy within a single transaction. When the transaction is finally committed,  $\gamma_2$  and  $\gamma_3$  are first invalidated. Next,  $\langle \gamma_0, \Phi_w, \gamma_1 \rangle$  is copied over  $\langle \gamma_2, \Phi_p, \gamma_3 \rangle$ . If this copy operation completes successfully, canaries  $\gamma_2$  and  $\gamma_3$  will be automatically restored (Listing 2).

#### **Listing 2** Update filesystem persistent copy.

```

procedure FsCommit  \gamma_2 \leftarrow False \qquad \qquad \triangleright aborted(PostCritical) \ (\neg aborted(PreCritical)) \\  \gamma_3 \leftarrow False \\  \langle \gamma_2, \Phi_p, \gamma_3 \rangle \leftarrow \langle \gamma_0, \Phi_w, \gamma_1 \rangle \\ \mathbf{end} \ \mathbf{procedure}

```

The presence of comments in the pseudocode, like "aborted(PostCritical) (¬aborted(PreCritical))" on the right side of the first line indicates that the referenced propositions hold after that line has completed its execution. These propositions are described in §3.4.

Figure 3.4: Prototype hardware components and interconnects.

When the processor boots up, it initializes the filesystem, which involves checking the canaries (Listing 3). At most one copy will have invalid canaries, and the other copy would then be used to restore the invalid copy. If both sets of canaries are valid, but the filesystem data is not identical, the persistent copy will be used to restore the working copy.

```

Listing 3 Initialize CAK filesystem.procedure FsInitif \langle \gamma_2, \gamma_3 \rangle \neq \langle True, True \rangle then\Phi_p \leftarrow \Phi_welse if \Phi_w \neq \Phi_p then\Phi_w \leftarrow \Phi_pend ifend procedure> sff-inited

```

The application firmware upgrade process is also fault-tolerant, but has significantly different fault-tolerance semantics than the filesystem. Two firmware regions are maintained in the system's flash. The upgrade region is used to store a firmware upgrade as it is uploaded. The installed region is the region actually executed when the application firmware is active. The commit process sequentially swaps pages in the two regions, using a page-sized staging area elsewhere in kernel program memory (Listing 4). The data in the two regions has been completely swapped at the end of the commit process. A status value  $\sigma_{upg}$  is stored in the filesystem and updated as the commit process progresses to enable recovery after a power failure that interrupts the process.

Every time the meter boots, the processor immediately transfers control to

## **Listing 4** Load firmware upgrade into executable space.

```

procedure UpgradeCommit

while \sigma_{upg}.n < pagecnt do

\triangleright n is initialized to 0 when an upgrade

is first initiated, and is not reinitialized here, because it is used to recover from

unexpected interruptions in the upgrade process.

if \sigma_{upg}.stage = Staging then

▶ stage is initialized to Staging when an

upgrade is first initiated.

codeStagingArea \leftarrow upgradeRegion_n

\sigma_{upg}.stage \leftarrow BackingUp

FsCommit

else if \sigma_{upg}.stage = BackingUp then

upgradeRegion_n \leftarrow installedRegion_n

\sigma_{upg}.stage \leftarrow Finishing

FsCommit

else if \sigma_{upg}.stage = Finishing then

installedRegion_n \leftarrow codeStagingArea

\sigma_{upg}.n \leftarrow \sigma_{upg}.n + 1

\sigma_{upg}.stage \leftarrow Staging

FsCommit

end if

end while

\sigma \leftarrow TestingUpgrade

FsCommit

end procedure

```

the Dirinit procedure in the CAK (Listing 5). The CAK first initializes the memory protections, performs filesystem recovery if necessary, and completes the application firmware upgrade transaction if one was interrupted by a power failure. It then generates a cryptographic hash of the firmware and compares it to the latest audit log entry. If they differ, it extends the log with a new entry. Finally, it transfers control to the application.

**Listing 5** Initialize director upon system reset.

```

procedure DirInit

FsInit

if IsUpgrading then

UPGRADECOMMIT

end if

if \sigma = Init \vee \sigma = Idle then

DirPrep(None, Idle)

else if \sigma = Upgrading then

DIRPREP(UpgradeAborted, Idle)

else if \sigma = TestingUpgrade then

DIRPREP(None, WaitingForHB)

else if \sigma = WaitingForHB then

DIRPREP(UpgradeHBFailed, Idle)

end if

end procedure

procedure DirPrep(\eta, \sigma^+)

\sigma \leftarrow \sigma^+

FsCommit

if \eta \neq None \vee |AL_{inmem}| = 0 \vee \epsilon_{n-1} \neq \langle \eta, h(\mathcal{F}_n) \rangle then

LogExtend(\langle \eta, h(\mathcal{F}_n) \rangle)

FsCommit

end if

JUMPMAIN

▶ appfw-active

end procedure

```

Both fault-tolerance processes are analyzed in §3.4 to ensure that the particular memory manipulations they use correctly recover from accidental power supply interruptions.

# 3.3 CAK Implementation and Evaluation

In this section we present CRAESI, a prototype standalone CAK. The purpose of this prototype is to demonstrate that our design satisfies the practical requirements put forth in §3.2, and to obtain preliminary performance, cost, and power-consumption measurements. However, these preliminary measurements do not indicate the parameters that will be exhibited by commercial implementations, since our prototype relies heavily on unoptimized software.

### 3.3.1 Hardware Components

Our prototype implementation comprises five distinct devices. The first is an Atmel ATSTK600 development kit containing an AT32UC3A0512 AVR32 microcontroller with a 3.3V supply voltage. The second device is a Schweitzer Engineering Laboratories SEL-734 substation electrical meter. The SEL-734 has a convenient RS-232 Modbus data interface. We could have used any similar device in our experiments since it simply serves as a realistic data source connected to the AVR32 microcontroller. Third, we use a standard desktop PC to communicate with the AVR32 microcontroller over an RS-232 serial port from a Java application that issues Modbus commands. The final two devices are paired ZigBee radios that relay RS-232 data between the PC and AVR32 microcontroller.

# 3.3.2 Application Firmware

We prepared two application firmware images for our experiments. They both implement Modbus master and slave interfaces, where the master communicates with the meter over an RS-232 serial port, and the slave accepts commands from the PC over the ZigBee link and either passes them to the kernel or handles them directly if they are requesting data from the meter. The first image accurately relays meter data, whereas the second halves all meter readings, as might be the case with a malicious firmware image installed on an advanced meter by an unethical customer.

CRAESI would interfere with the operation of existing embedded operating systems that require access to security-critical peripherals and memory areas. However, virtualization techniques could be used to accommodate those accesses, given sufficient resources to implement the virtualization.

| Module              | Lines of Code |

|---------------------|---------------|

| Core                | 810           |

| Crypto              | 5684          |

| Filesystem          | 160           |

| Hardware Management | 256           |

| TOTAL               | 6910          |

Table 3.1: Lines of C++ code in each CRAESI kernel component.

#### 3.3.3 Kernel Firmware

The kernel is invoked whenever the processor resets, and by the application firmware when required. The AVR32 scall instruction is used to implement a syscall-style interface between the application and kernel. TinyECC provides software implementations of SHA-1 hashing and Elliptic Curve Cryptography (ECC) [48]. Pseudo-random numbers are generated by Mersenne Twister [49]. These libraries are not significantly optimized for AVR32. Note that the algorithms and key lengths used here may not be suitable for production use in systems with extended lifetimes during which the algorithms may be compromised. A commercial implementation would require a true random number generator. Table 3.1 provides a breakdown of the lines of C++ code in each kernel component. These numbers were generated from the raw source code directories, which include debugging and unused code. We exclude the drivers provided by Atmel.

The kernel consumes 81,312 bytes of program memory. We reserved 88KiB of flash memory to store the kernel code, and another 40KiB to store the persistent data manipulated by the kernel. We set aside 12KiB of data RAM for the kernel comprising 10,872 bytes of static data, 392 bytes for the heap, and 1024 bytes for the stack. The memory consumed by the kernel is unavailable to the application, which does impose an added cost if it becomes necessary to upgrade to a larger microcontroller than would have been required without the kernel. In this prototype, the maximum application firmware image size is 191.5KiB. However, commercial kernel implementations will be significantly more compact in both flash and data RAM than our unoptimized prototype, and clever swapping schemes could potentially eliminate the data RAM consumption of the kernel when it is not active. The audit log in this implementation can record up to 107 upgrades and events before overflowing.

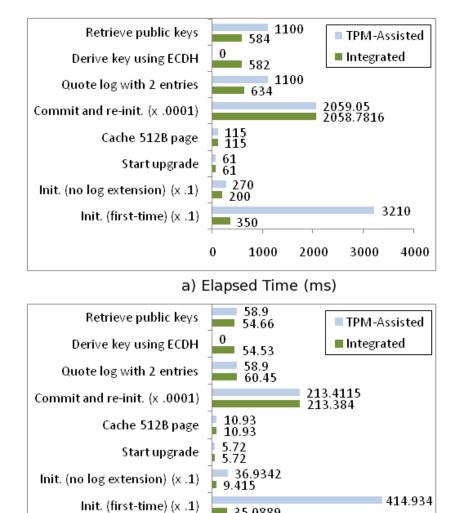

b) Energy Consumed (mJ)

35.0889

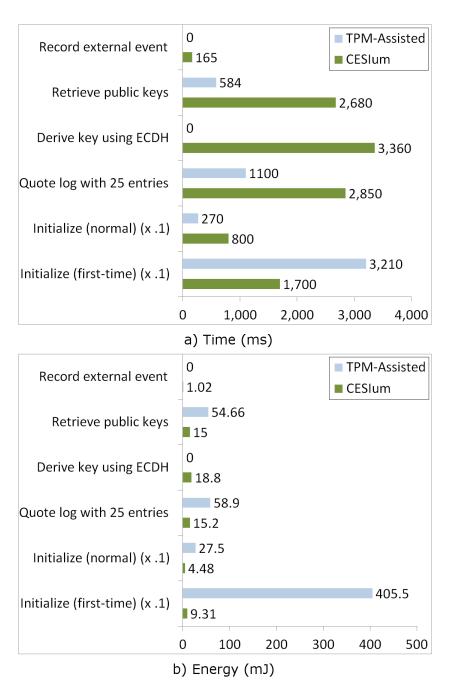

Figure 3.5: A performance comparison of TPM-assisted and standalone (integrated) CRAESI.

#### 3.3.4 Performance Results

We now compare the energy and time consumed by our firmware-only prototype (integrated CRAESI) to that consumed by an Atmel AT97SC3203 TPM performing comparable operations (TPM-assisted CRAESI). We used a TPM installed in a PC to perform similar operations to those that would be required by TPM-assisted CRAESI if it were actually implemented. The TPM has a supply voltage of 3.3V and relies on an LPC bus connection. We used Digital Multi-Meters (DMMs) that have limited sampling rates (100-300 ms between samples) to measure the energy consumption of both systems. This introduces some error into our calculations, so we have presented an upper-bound on the energy consumed by integrated CRAESI and a lower-bound on the energy consumed by TPM-assisted CRAESI. The time and energy consumed for a variety of operations is presented in Figure 3.5. From the figure, it is clear that the performance of CRAESI is comparable to a TPM executing similar operations, with the exception of the initialization routines that are much more expensive on a TPM for unknown reasons.

The TPM uses a 2048-bit RSA key to sign the PCRs, which provides security roughly equivalent to that of a 224-bit ECC key, superior to the security of the 192-bit ECC keys used in integrated CRAESI [70]. Due to the use of hardware, the TPM RSA signature generation mechanism is roughly as energy consumptive as the ECC software implementation in the integrated design. The Elliptic-Curve Diffie-Hellman (ECDH) key exchange supported by integrated CRAESI would not be supported by TPM-assisted CRAESI, although it could potentially be replaced with equivalent functionality.

The most significant efficiency drawback of the TPM is that it demands 10.6mW when sitting idle. It may be possible to place the TPM into a deep sleep state to reduce this constant burden, but that is not done in practice in our test system, and may have unexamined security consequences. Let us consider the practical implications of this overhead if attestation is performed once per day per meter in an installation containing five million meters. If AT97SC3203 TPMs were installed in all of those meters, they would consume at least 466,908 kWh per year. In contrast, if integrated CRAESI were used instead, it would consume less than 31 kWh per year.

# 3.4 CAK Correctness and Fault-Tolerance Analysis